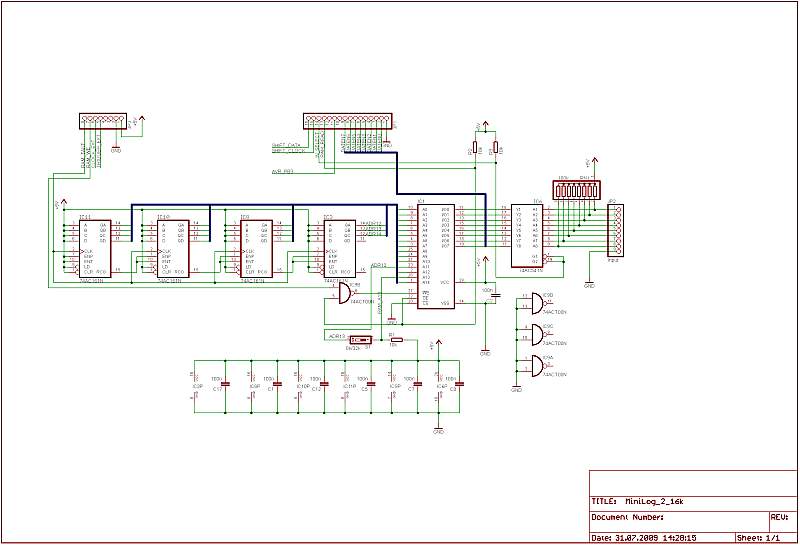

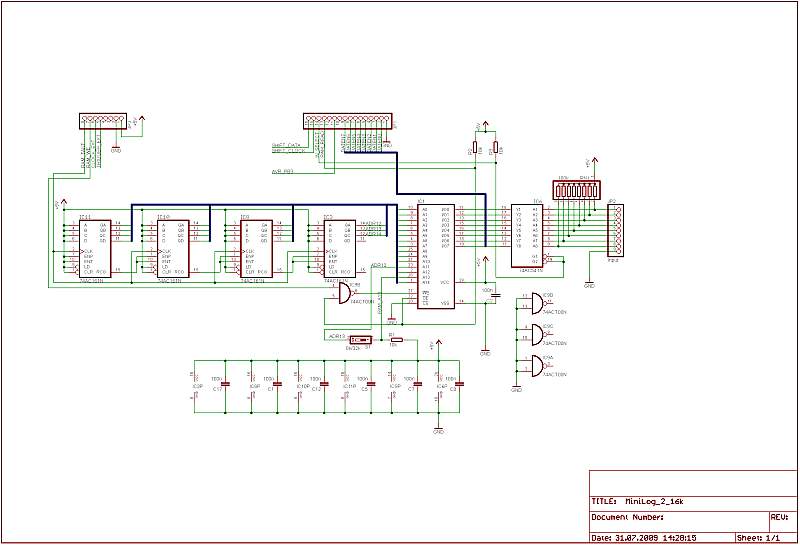

AVR - Basteleien - Logic-Analyzer MiniLog - Hardware

1. Version:

Stand der Dinge:

Hardware:

8 Kanäle, max. 50MSample/s, 4000 Sample Speicher, Trigger auf beliebige Pegelkombinationen

Erweiterung auf max. 8 oder 32k Samplespeicher wäre problemlos möglich (1x 74ACT161), auch die Anzahl der Kanäle könnte auf 16 (oder mehr...) erweitert

werden (je 8 Bit ein Cacheram und ein bi-directionaler TriState-Bustreiber). Das ist aber völlig ungetestet, müßte aber gehen.

80MHz Samplerate waren beim Lochrasteraufbau nicht stabil, deshalb erstmal 50MHz.

Kosten?

Teile lagen fast alle noch bei mir rum, der TTL-Kram wohl so 4 Euro,

der AVR (ja, der Mega644 ist völlig überdimesioniertm war aber der Einzige, der rumlag und mit 20MHz Takt war und genug Portpins hatte...)

Kleinkram, Quarzoszillatoren usw. usw.

Je nach Vorräten also wohl so 20 Euro. Als USB-Adapter geht jeder, der TTL kann oder man hat noch eine serielle und lötet einen MAX232 dran...

(erstmal) fertig...

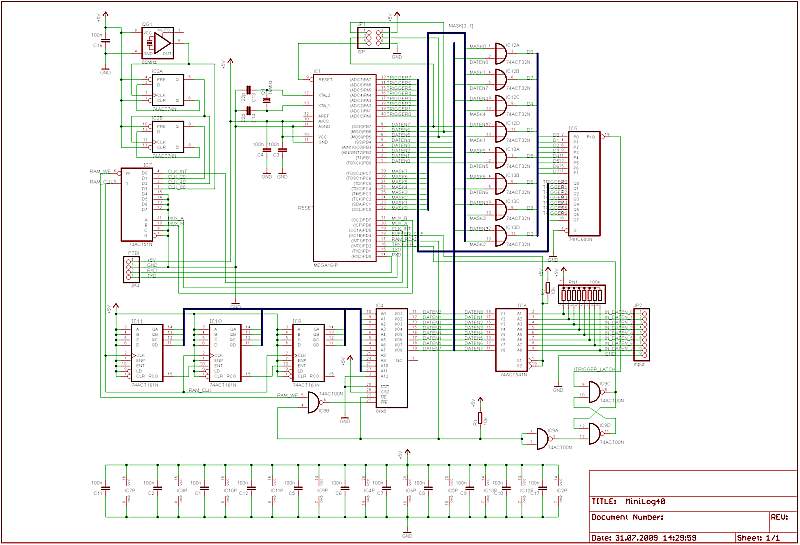

Zum Hardwarekonzept:

Ein entsprechend schneller Takt (1kHz (1ms) ... 10Mhz (100ns vom AVR, 20MHz (50ns) und 50MHz (20ns) von Quarzoszillatoren)

läßt mit einen Syncron-Zähler (3x 74ACT161) die Ram-Adressen durchzählen.

Die Umschaltung AVR/Quarzoszillatoren erledigt ein 1 aus 8 MUX (74ACT151). Dort sind z.Z. nur 2 Adressen genutzt, also 4 Taktquellen wählbar.

Der invertierte Zählertakt ist auch /WE des Rams. Der Ram ist ein (früher mal...) üblicher Cache-Ram 8kx8 mit 12ns.

Es werden nur 4kB genutzt, der Adresszähler hat ja (zur Zeit) nur 12 Bit.

Es wird entweder ständig geschrieben (wenn der AVR über den MUX den Takt freigibt) oder gelesen (dann taktet immer der AVR).

Die Eingangsdaten gehen über einen Buspuffer (74AC541), direkt am Eingang sind 100k PullUp, damit offene Leitungen einen definierten Pegel anzeigen.

Die Triggerlogik besteht aus einem 8Bit-Vergleicher (74HC688). Dort liegt einmal das Triggerbyte vom AVR an, andererseits die Daten, die auch der Ram einliest. Die Daten gehen über 8 OR-Gatter (2x 74HCT32), damit können Bits ignoriert werden.

Low vom Ausgang des Vergleichers setzt ein RS-Flip-Flop und meldet das dem AVR.

Die Ablaufsteuerung erledigt der AVR, zum PC geht es mit 115200 Baud über einen FT232R mit USB zum PC. Dort wird ein virtueller COM-Port benutzt.

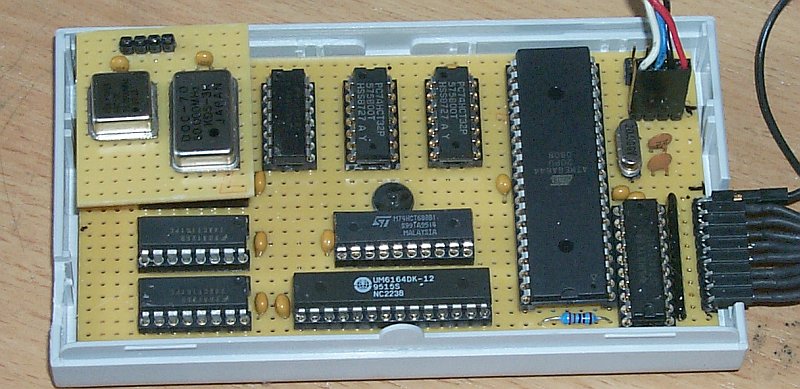

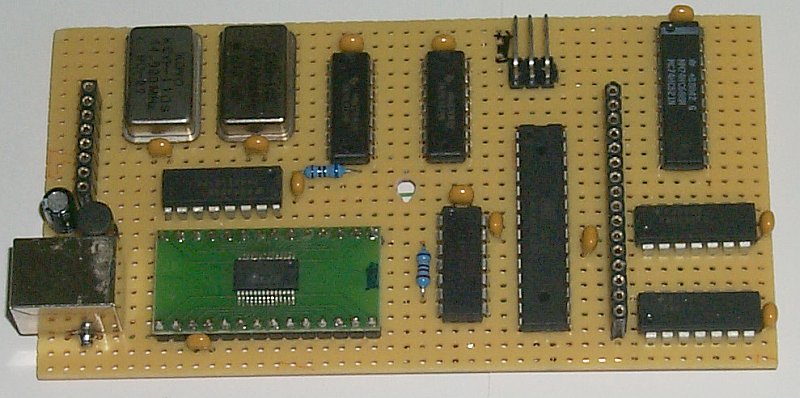

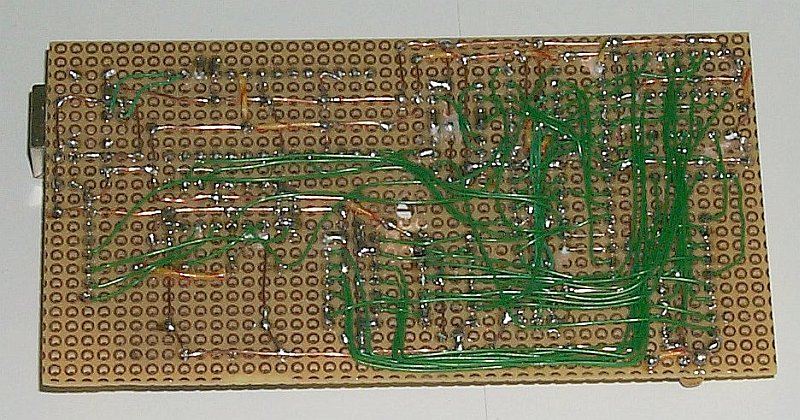

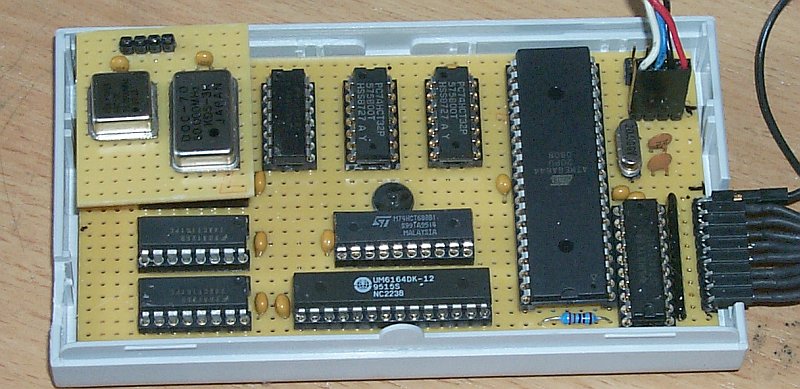

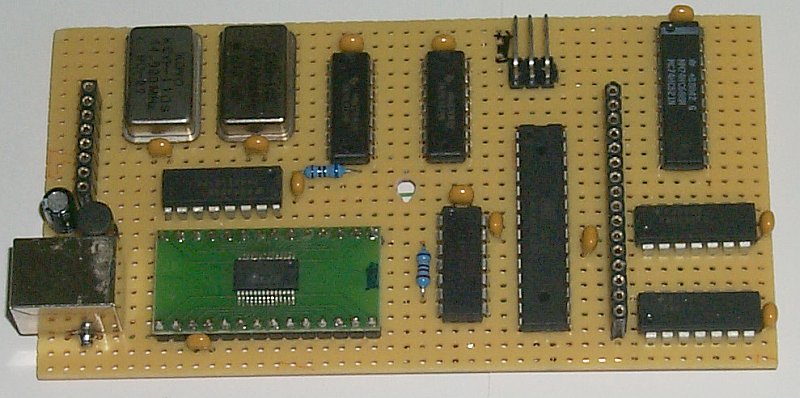

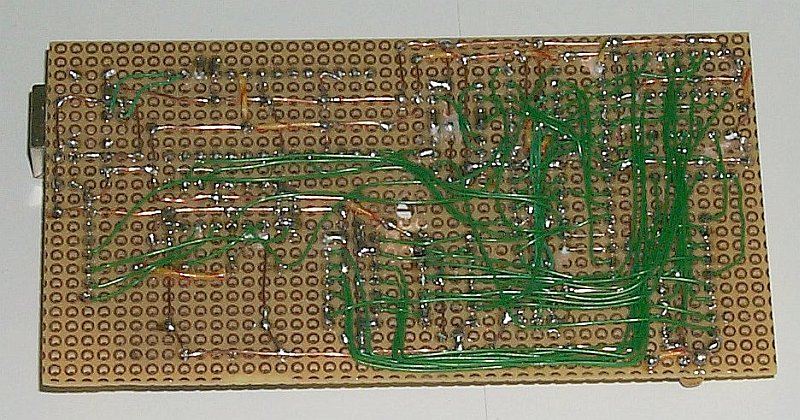

Aufbau (wie bei mir üblich...) auf Lochraster. Ja, auch 50MHz gehen damit!

Neu! Hardware MiniLog80 - die 80MHz Version auf Basis der ersten Hardware

Die Geschichte läuft jetzt stabil.

Geändert wurde nur das "Taktmodul", da wohnt jetzt ein 80MHz Oszillator und ein 74ACT74 als 4:1 Teiler drauf.

Die Takte 80MHz, 40MHz und 20MHz kommen von dort, 8MHz und weniger liefert der Mega16.

Die Staffelung ist dadurch 80-40-20-8-4-2 usw., damit reicht ein Takt von 16MHz für den AVR.

Auch diese Version überträgt zum PC jetzt natürlich mit 500000 Baud.

Probleme:

Die Adress-Zähler sind bei 80MHz an ihrer Grenze (und/oder der Aufbau).

Die Leitungen PE der 74ACT161 müssen fest auf H, nicht wie in der ursprünglichen Schaltung zusammen mit TE an Carry-Out.

Sonst zählen die hinteren Zähler nur noch manchmal mit. Interessant war dabei, daß sie nicht etwa Impulse wegliessen,

sondern entweder einer oder beide garnicht zählten.

Wenn sie zählte dann zählten sie richtig...

Die Änderung brachte jedenfall die fehlenden Nanosekunden.

Da nur 3 Adresszähler verbaut sind und kein Platz mehr ist, bleibt es auch bei einem 8k-Ram, von dem 4k genutzt werden.

Achtung! um den Überblick wiederzugewinnen heißen die Pläne mit dem ATMega16 jetzt MiniLog40 für 40-Pin-AVR

Eagle 5.x Schaltpläne aktuell:

Schaltplan

Hardware 80MHz Version

Schaltplan 80MHz Version

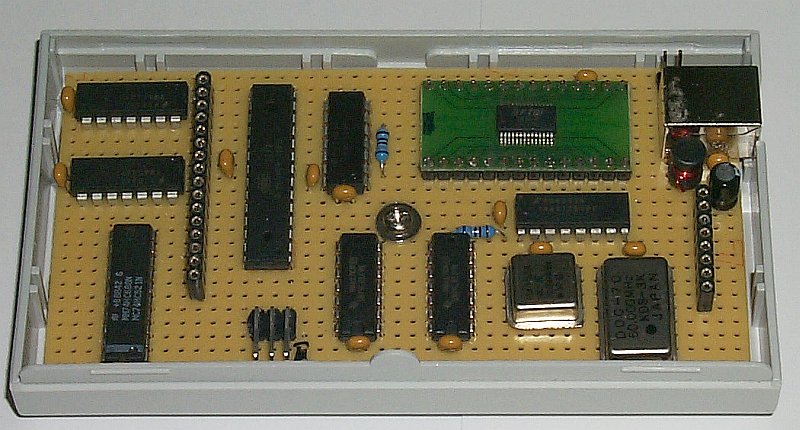

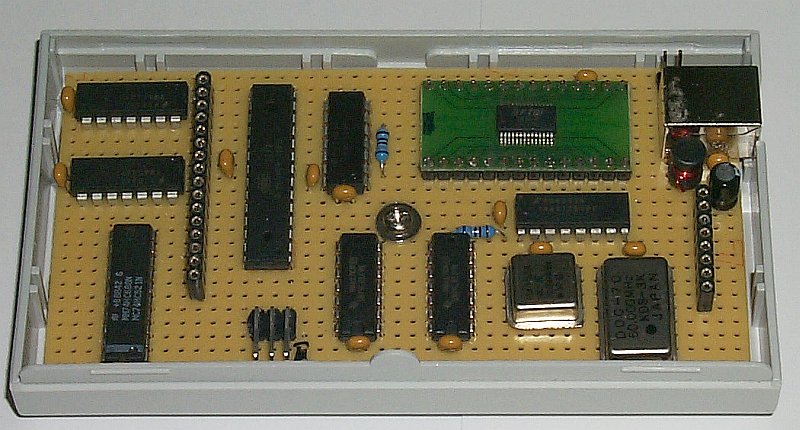

Gehäuse offen

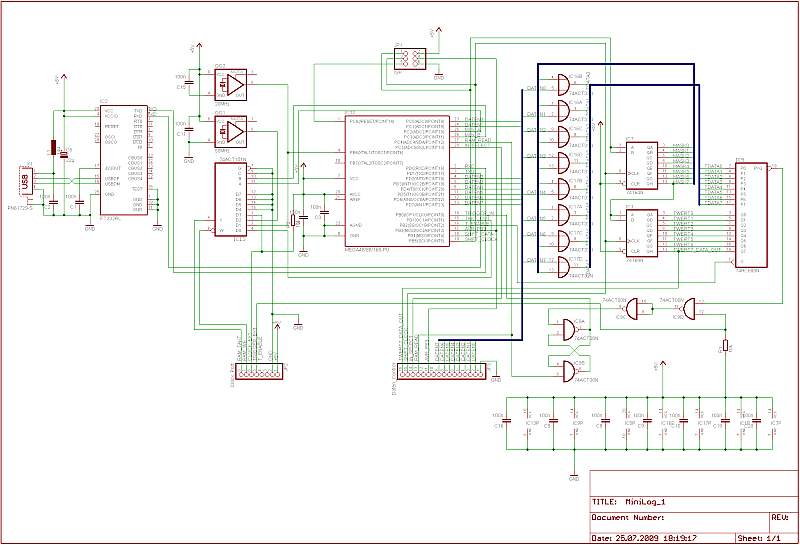

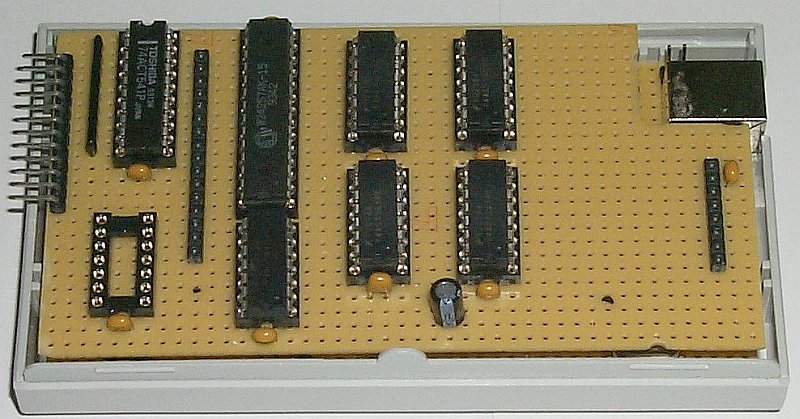

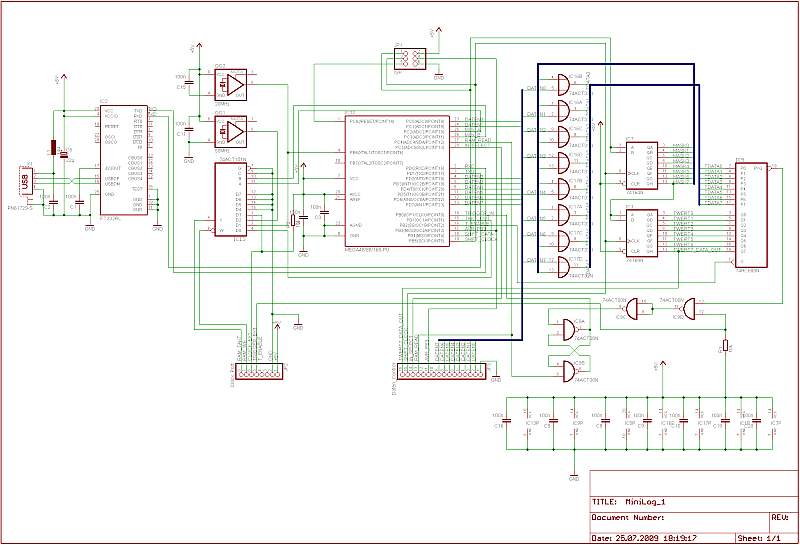

Neue Version:

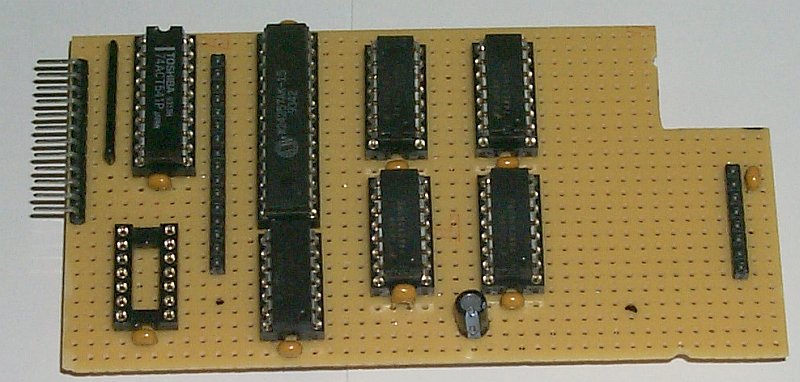

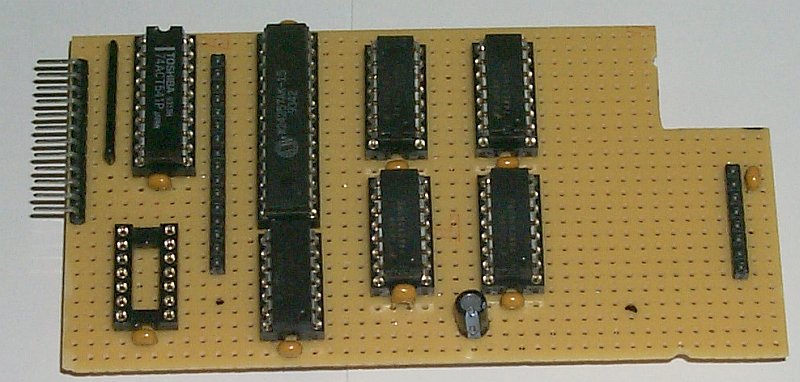

Eigentlich nur neuer Aufbau.

AVR ist jetzt ein Mega88 (Mega48 reicht auch, hatte ich gerade nicht da).

Samplespeicher jetzt 16k (eigentlich 32k, die VB-Software maß da aber noch etwas umgebaut werden).

Schaltplan AVR, Trigger und Takt

Schaltplan Ram, Zähler und Eingangt

Achtung! um den Überblick wiederzugewinnen heißen die Pläne mit dem ATMega88 jetzt MiniLog28 für 28-Pin-AVR

Änderung! Pin 1 (/G) vom 74H688 geht jetzt an PB2 des AVR!

Eagle 5.x Schaltpläne aktuelle Version:

Schaltpläne

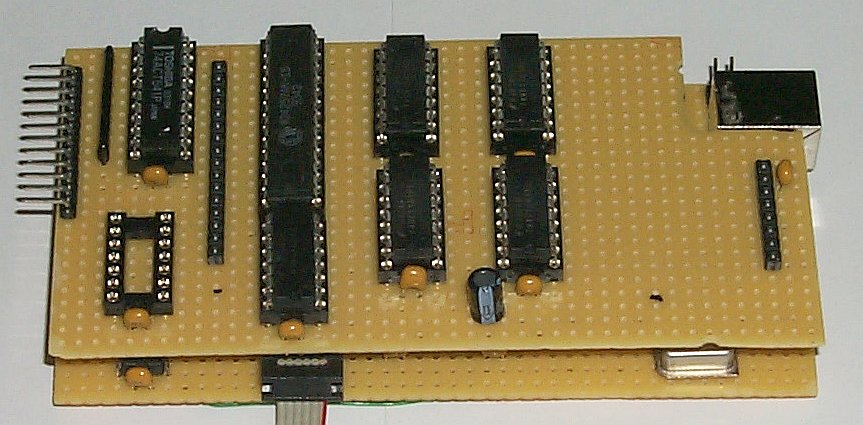

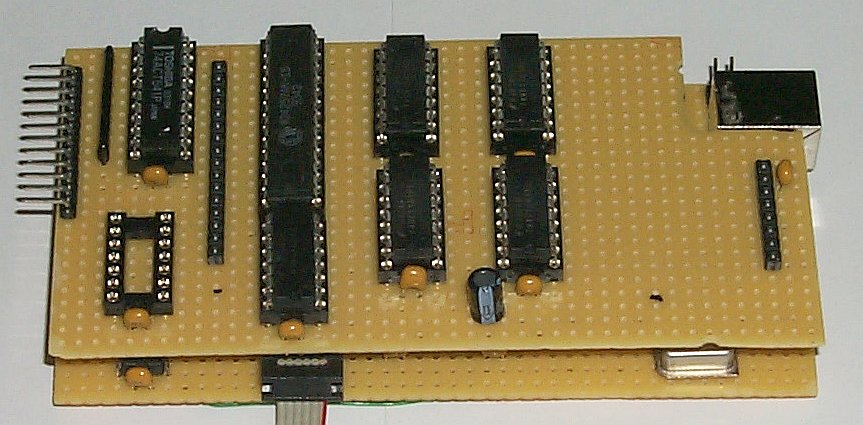

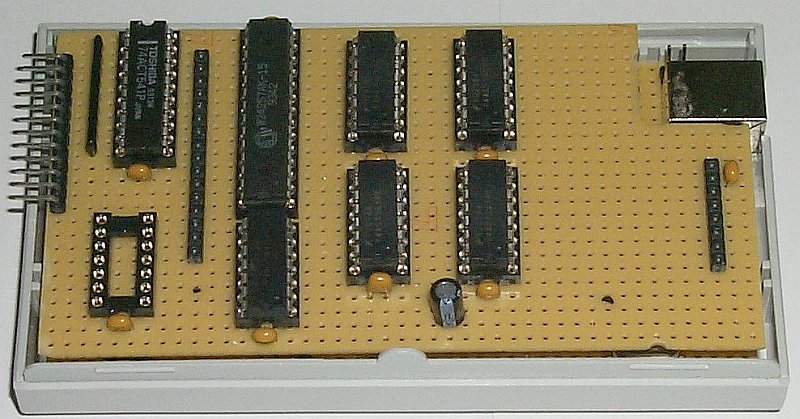

AVR-Logikteil

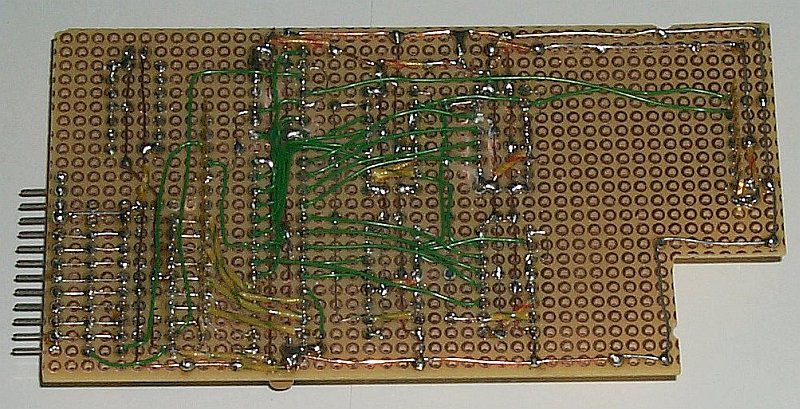

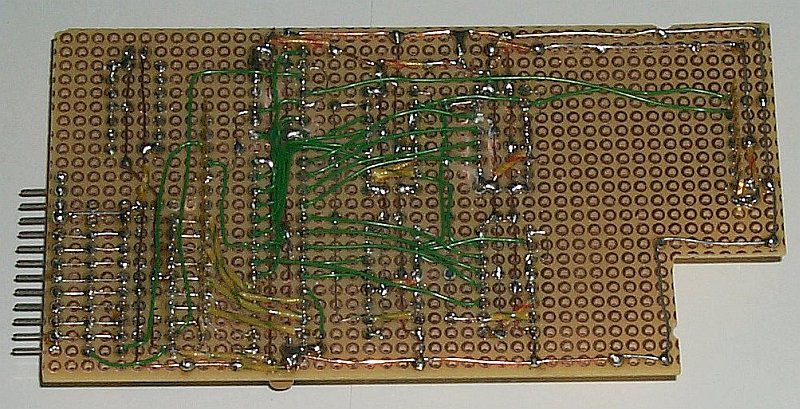

...und von unten

Ram und Adresszähler

...und von unten

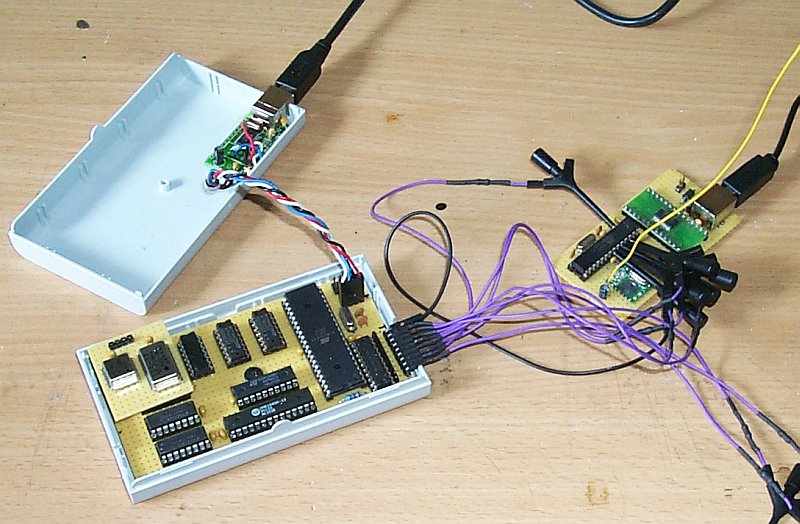

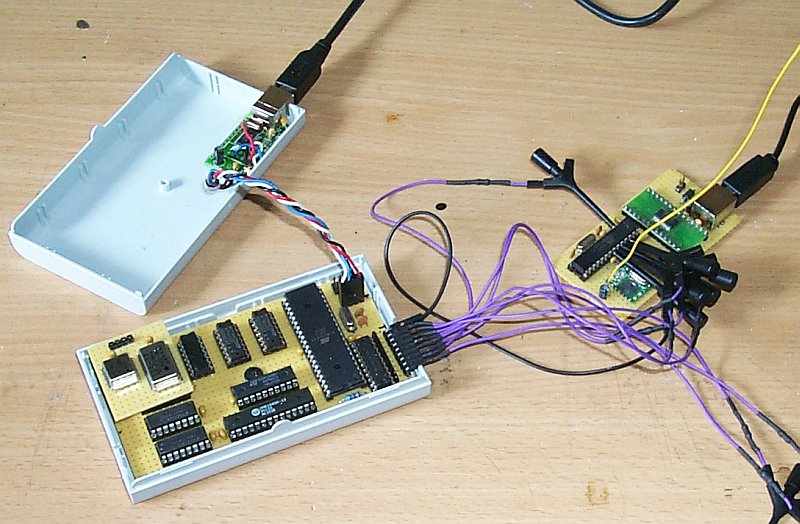

zusammengestckt (mit ISP-Kabel dran)

Im Gehäuse befestigt

und zusammengesteckt

Bei Fragen entweder eine E-Mail schicken.

Erstmal keine Lust mehr heute..... ;-)

Letzte Änderung am 31.07.2009